# カーボンナノチューブ FET のアナログ回路設計モデルに関する検討

薬師寺勇健 \* 宮内亮一 \*\* 外山貴子 \*\*\* 田村宏樹 \*\*\* 淡野公一 \*\*\* (宮崎大学\*大学院工学研究科\*\*大学院農学工学総合研究科\*\*\*工学部)

## 1 はじめに

LSI の主要な素子である MOSFET の微細化はリーク 電流の増大や真性利得の低下といった問題を引き起こし、 今日の集積技術の発展における制約となっている.

これらの問題を解決するデバイスとして近年カーボン ナノチューブ FET (Carbon-Nanotube Field Effect Transistor:CNFET) が注目されている.CNFET はリーク電 流の抑制に有効な構造と、バリスティック伝導による高い 電流駆動能力を有し, Stanford 大学から SPICE モデルが 公開されている[1]. CNFET の応用はデジタル回路に関 するものが多く,アナログ回路への応用は少ない.これは Stanford CNFET Model の電流式に MOSFET のような 設計パラメータが含まれていないことが原因と考えられる.

そこで本論文では、CNFET を MOSFET と同様に扱う ことのできるアナログ回路設計モデルを提案する.また, 提案モデルを使用し,アナログ要素回路の一つである差動 増幅回路 (DA) を設計し,モデルの有用性を確認する.

## 2 CNFET の特性解析

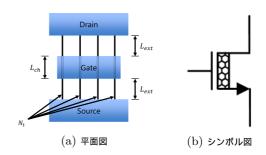

図 1 に CNFET の構造を示す . 図 1a 中の  $N_t$ ,  $L_{ch}$ ,  $L_{ext}$ はそれぞれチューブ数,チャネル長,ゲート-ドレイン間 (ゲート-ソース間)の長さを表し,これらが CNFET に おける設計パラメータとなる.

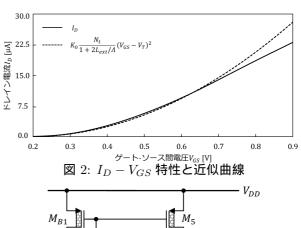

$\mathrm{CNFET}$  の飽和電流  $I_D$  は  $\mathrm{MOSFET}$  との類似性および 設計の容易性から,二乗則で近似できると仮定した.これ より式 (1) に示す近似式が得られる ( $K_0$  は比例定数).

$$I_D = K_0 \frac{N_t}{1 + 2L_{ext}/\Lambda} (V_{GS} - V_T)^2 \tag{1}$$

図 2 に CNFET の  $I_D - V_{GS}$  特性および式 (1) による近似 曲線を示す. 図中の実線は実際の電流値, 破線は近似値を 表す.この図から,0.2~0.7 V の区間では誤差が小さく, 比較的問題なく使用できると思われる.

## 3 シミュレーション結果

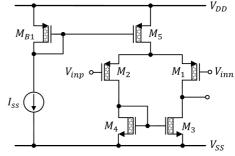

式(1)を用いて DA を設計し,シミュレーションを行っ た.シミュレーションには Stanford CNFET Model を用 いる.回路構成を図3に示す.MOSFETと同様にトラン スコンダクタンス  $g_m$  およびドレインコンダクタンス  $g_d$  を 次式のように定義する.

$$g_{m} = \frac{\partial I_{D}}{\partial V_{GS}}$$

$$g_{d} = \frac{\partial I_{D}}{\partial V_{DS}}$$

(2)

$$g_d = \frac{\partial I_D}{\partial V_{DG}} \tag{3}$$

式 (2), (3) を用いて  $g_m$ ,  $g_d$  を計算し,直流利得の算出を 行った.表1に計算値とSim 値の比較を示す.表1より, 計算値と Sim 値の誤差は 10% 未満となることが分かる .

### 4 まとめ

本論文では, CNFET をアナログ回路に応用することを 目的に MOSFET と同様に扱うことのできるアナログ回

路設計モデルとそれを適用した DA 回路の設計について 述べてきた.シミュレーションの結果より,本モデルを用 いることで誤差率 10 % 未満の精度で設計が可能であるこ とを確認した,今後の課題は二段構成オペアンプやその他 の要素回路への本モデルの適用が考えられる.

図 1: CNFET の構造

図 3: 差動増幅回路

表 1: DA の測定結果

| 項目                  | 計算値  | Sim 値 | 誤差率 [%] |

|---------------------|------|-------|---------|

| $g_{m1}$ [ $\mu$ S] | 149  | 142   | 4.93    |

| $g_{d1}$ [nS]       | 10.4 | 10.4  | 0.00    |

| $g_{d3}$ [nS]       | 5.25 | 5.25  | 0.00    |

| 直流利得 [倍]            | 9549 | 9120  | 4.70    |

### 参考文献

[1] J. Deng, H.S.P. Wong, "A compact SPICE model for carbon-nanotube field-effect transistors including non idealities and its application-part I: Model of the intrinsic channel region," IEEE Trans. on Electron Devices, vol. 54, no. 12, pp. 3186-3194.